USB DAQ Firmware, 2.0 Release, Major Features

USB DAQ Firmware, 2.0 Release, & Major Features

THE LATEST ROUND OF FIRMWARE UPDATES FOR THE USB DAQ PRODUCT LINE HAS ARRIVED!

This new firmware release takes advantage of the local intelligence built into these USB Test and Measurement devices by implementing a number of new capabilities, including Watchdog, PWM, Low-Pass digital filtering, and more.

Features

- Features common to all Firmware 2.0 devices

- WDG: Watchdog Timer – If your application fails to communicate with (pet) the device before the watchdog times out (barks) all outputs will assert whatever values you configure.

- DEF: Power-On-Defaults – Modify the factory-set power-on values for all outputs or I/O.

- Digital Input Features

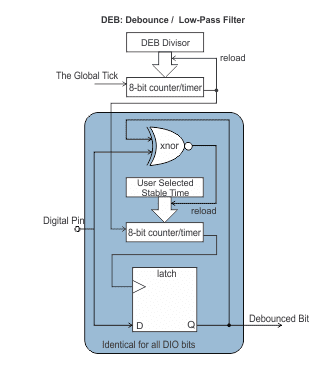

- DEB: Debounced Digital Inputs – low pass filtering for digital input bits. Time constants from microseconds to seconds.

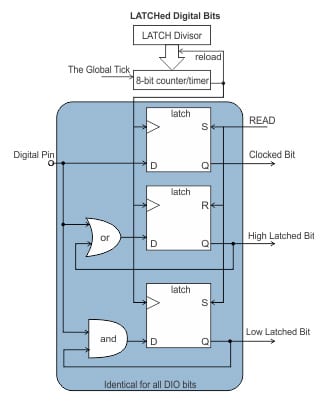

- LATCH: High and Low digital input Latching – onboard intelligence will monitor the input bits, and record if they’ve been low — AND if they’ve been high — since your application last queried.

- Digital Output Features

- MAP: Matrix Mapping – command the onboard intelligence to periodically copy input states to output bits.

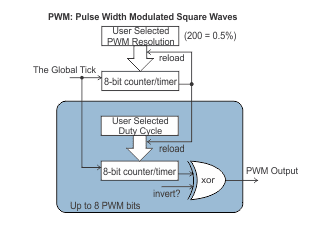

- PWM: Pulse Width Modulation – programmable duty cycle square wave output, with resolution better than 0.5%

Watchdog Timers consist of three facets: the timeout period, the “pet” action, and the “bark” action. The timeout period in the Firmware 2.0 release can be specified in seconds, between one and 65535 seconds. The pet action is defined as any successful communication with the USB device’s command interface. This means any usb_control_transfer that successfully addresses the onboard commands. The bark action in the Firmware 2.0 release can control the I/O direction of digital ports, as well as the output value of all output bits, DACs, and counter-timers. A very common use of the bark action would be turn off external devices such as fans, conveyor belts, heating elements, etcetera, to avoid out of control operation if the computer is locked up or otherwise unavailable. A less obvious application would use a spare output bit: by commanding the bit to go active as part of the bark action you have a signal to the real world that the controlling computer isn’t working correctly.

Configurable power on default values allows you to set the various board configuration parameters the way you want them, once, then store this configuration in the onboard non-volatile memory for automatic use at every reset or power-on. Nearly everything about the devices can be configured, including the configuration of Firmware 2.0 features like Debouncing and PWM bits. You can customize the power-on state either using your own software or a provided configuration utility.

Debouncing provides a way to avoid the vagaries of mechanical contact bounce from confusing your software and users. By commanding the onboard intelligence to monitor the inputs and filter out contact bounce you avoid needing to add low-pass filtering circuits to each of your button and relay digital inputs. Firmware 2.0 allows flexible debouncing time constants from tens of microseconds to hundreds of milliseconds, per bit, compatible with the widest variety of contact closures, on all digital bits of each device.

Debouncing provides a way to avoid the vagaries of mechanical contact bounce from confusing your software and users. By commanding the onboard intelligence to monitor the inputs and filter out contact bounce you avoid needing to add low-pass filtering circuits to each of your button and relay digital inputs. Firmware 2.0 allows flexible debouncing time constants from tens of microseconds to hundreds of milliseconds, per bit, compatible with the widest variety of contact closures, on all digital bits of each device.

Latching allows your software to relax, and let the onboard intelligence obsess over catching that pulse — and can make noticing shorter pulses trivial instead of virtually impossible. The Firmware 2.0 release can simultaneously perform low-side and high-side latching of all digital inputs, clearing the latches only when your application gets around to reading them. The onboard intelligence can read the digital inputs faster than once every 100 microseconds without consuming any CPU cycles from your host computer.

Latching allows your software to relax, and let the onboard intelligence obsess over catching that pulse — and can make noticing shorter pulses trivial instead of virtually impossible. The Firmware 2.0 release can simultaneously perform low-side and high-side latching of all digital inputs, clearing the latches only when your application gets around to reading them. The onboard intelligence can read the digital inputs faster than once every 100 microseconds without consuming any CPU cycles from your host computer.

Latching allows your software to relax, and let the onboard intelligence obsess over catching that pulse — and can make noticing shorter pulses trivial instead of virtually impossible. The Firmware 2.0 release can simultaneously perform low-side and high-side latching of all digital inputs, clearing the latches only when your application gets around to reading them. The onboard intelligence can read the digital inputs faster than once every 100 microseconds without consuming any CPU cycles from your host computer.

PWM output bits generate square waves, with configurable duty cyle andpolarity. Up to 8 digital outputs can be performing PWM output at the same time, per device.

PWM output bits generate square waves, with configurable duty cyle andpolarity. Up to 8 digital outputs can be performing PWM output at the same time, per device.

Implementation and Limits

THE GLOBAL TICK

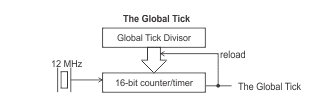

An onboard periodic IRQ generator creates one Global Tick IRQ at a rate you can configure, based on a 16-bit divisor of an internal 12MHz clock. This allows the Global Tick IRQ to occur at rates as slow as 183Hz, or as fast as 10kHz or more. Each Firmware 2.0 feature operates either on every Global Tick, or on a tick derived from a further 8-bit division of this rate.

An onboard periodic IRQ generator creates one Global Tick IRQ at a rate you can configure, based on a 16-bit divisor of an internal 12MHz clock. This allows the Global Tick IRQ to occur at rates as slow as 183Hz, or as fast as 10kHz or more. Each Firmware 2.0 feature operates either on every Global Tick, or on a tick derived from a further 8-bit division of this rate.

DEF – power-on defaults stores these divisors, but it only operates when commanded, not per any given tick.

WDG – Watchdog operates on a One Second tick, and counts down your configured timeout period before barking

DEB – Debounced digital inputs use an a local tick and a time constant. You specify what division of the global tick should be used to create the Debounce Tick (divide by 1 through 255). On each Debounce Tick every digital bit on the device is read, and if it has been stable for as many Debounce Ticks as the time constant specifies, updates the “debounced” copy of the digital data.

LATCH – Latched digital inputs also use a local tick, specified as a further 8-bit (1-255) divisor of the global Tick. Each Latch Tick will cause all digital bits to be read, and evaluated for high-or-low, and stored. Reading Latched data provides three different pieces of information for each and every digital bit: the state of the bit at the most recent Latch tick, if the bit has been low since last read, and if the bit has been high since last read.